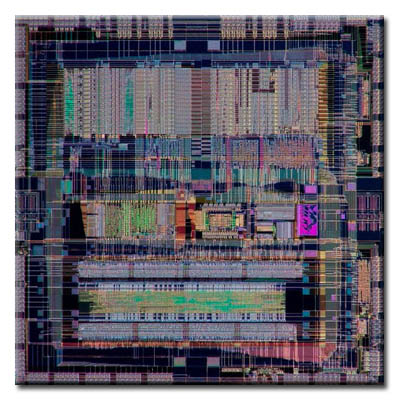

Hewlett Packard PA-7000 (Cheetah) processors

Introduction: 1991

The PA-7000 was the first PA-RISC 1.1 CPU implementation and saw its first uses in the first PA-RISC 700 series workstations and later on in some of the Nova servers. It was still a multi-chip implementation.

The PA-7000 was used in 705/35, 710/50, 720/50, 730/66, 750/66, F10, F20, F30, G30, G40, H20, H30, H40, I30 and I40.

Source: www.openpa.net