AMD Athlon 64 X2 (Manchester, Toledo, Windsor, Brisbane) processors

Introduction: May 2005 (Manchester and Toledo), May 2006 (Windsor), December 2006 (Brisbane)

Overview

The Athlon 64 X2 was the first dual-core desktop CPU manufactured by AMD. It was essentially a processor consisting of two Athlon 64 cores joined together on one die with additional control logic. The cores shared one dual-channel memory controller, were based on the E-stepping model of Athlon 64 and, depending on the model, had either 512 or 1024KB of L2 Cache per core. The Athlon 64 X2 was capable of decoding SSE3 instructions (except those few specific to Intel's architecture), so it was able to run and benefit from software optimizations that were previously only supported by Intel chips. This enhancement was not unique to the X2, and was also available in the Venice and San Diego single core Athlon 64s.

The Manchester, Toledo, Windsor and Brisbane cores

On April 21, 2005, less than a week after the release of Venice and San Diego, AMD announced its next addition to the Athlon 64 line, the Athlon 64 X2. Released on May 31, 2005, it also initially had two different core revisions available to the public, Manchester and Toledo, the only appreciable difference between them being the amount of L2 cache. Both were released only for Socket 939. A response to Intel's dual core Pentium D, the Athlon 64 X2 was received very well by reviewers and the general public, with a general consensus emerging that AMD's implementation of multi-core was superior to that of the Pentium D. Some felt initially that the X2 would cause market confusion with regard to price points since the new processor was targeted at the same "enthusiast," US$350 and above market already occupied by AMD's existing socket 939 Athlon 64s. AMD's official breakdown of the chips placed the Athlon X2 aimed at a segment they called the "prosumer", along with digital media fans. The Athlon 64 was targeted at the mainstream consumer, and the Athlon FX at gamers. The Sempron budget processor was targeted at value-conscious consumers.

The main benefit of dual-core processors like the X2 was their ability to process more software threads at the same time. The ability of processors to execute multiple threads simultaneously was called thread-level parallelism (TLP). By placing two cores on the same die, the X2 effectively doubled the TLP over a single-core Athlon 64 of the same speed. The need for TLP processing capability was dependent on situation to a great degree, and certain situations benefit from it far more than others. Certain programs were currently only written with one thread, and were therefore unable to utilize the processing power of the second core.

Programs often written with multiple threads and capable of utilizing dual-cores included many music and video encoding applications, and especially professional rendering programs. High TLP applications corresponded to server/workstation situations more than the typical desktop. These applications was able to realize almost twice the performance of a single-core Athlon 64 of the same specifications. Multi-tasking also ran a sizable number of threads; intense multi-tasking scenarios had actually shown improvements of considerably more than two times. This was primarily due to the excessive overhead caused by constantly switching threads, and could potentially be improved by adjustments to operating system scheduling code.

In the consumer segment of the market as well, the X2 improved upon the performance of the original Athlon 64, especially for multi-threaded software applications. The overall increased in performance of the entry level Athlon 64 X2 chip (the Athlon 64 X2 3800+) over the single-core Athlon 64 3800+ chip was almost 10%. The spread between the latter and the Athlon 64 X2 5000+ was almost 40%. One was able to interpret from these numbers that the majority of applications (at least in the benchmark test) were still largely single thread-dominated, hence the absence of a larger gap between the two 3800+ processors. As software programmers began to take advantage of multi-core processing, the spread between single- and multi-core processors increased.

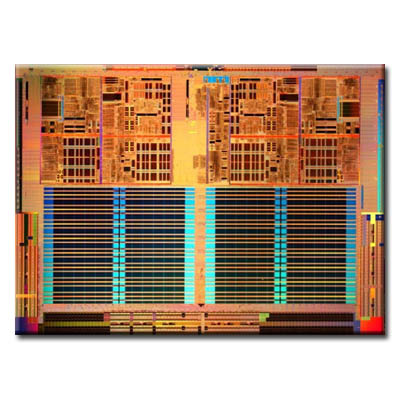

Having two cores, the Athlon 64 X2 had an increased number of transistors. The 1MB L2 cache 90 nm Athlon 64 X2 processor was 219 mm² in size with 243 million transistors whereas its 1MB L2 cache 90 nm Athlon 64 counterpart was 103.1 mm² and had 164 million transistors. The 65 nm Athlon 64 X2 with only 512KB L2 per Core reduced this to 118 mm² with 221 million transistors compared to the 65 nm Athlon 64 with 77.2 mm² and 122 million transistors. As a result, a larger area of silicon had to be defect free. These size requirements necessitated a more complex fabrication process, which further adds to the production of fewer functional processors per single silicon wafer. This lower yield made the X2 more expensive to produce than the single-core processor.

In the middle of June 2006 AMD stated that they would no longer make any non-FX Athlon 64 or Athlon 64 X2 models with 1MB L2 caches. This led to only a small production number of the AM2 Socket Athlon 64 X2 with 1MB L2 cache per core, known as 4000+, 4400+, 4800+, and 5200+. The Athlon 64 X2 with 512KB per core, known as 3800+, 4200+, 4600+, and 5000+, were produced in far greater numbers. The introduction of the F3 stepping then saw several models with 1MB L2 cache per core as production refinements resulted in an increased yield.

Source: Wikipedia, the free encyclopedia.