Intel Itanium (Merced) processors

Introduction: June 2001

Overview

Itanium was the brand name for 64-bit Intel microprocessors that implement the Intel Itanium architecture (formerly called IA-64). Intel had released two processor families using the brand: the original Itanium and the Itanium 2. Starting November 1, 2007, new members of the second family are again called Itanium. The processors were marketed for use in enterprise servers and high-performance computing systems. The architecture originated at Hewlett-Packard (HP) and was later developed by HP and Intel together.

Itanium's architecture differed dramatically from the x86 architectures (and the x86-64 extensions) used in other Intel processors. The architecture was based on explicit instruction-level parallelism, with the compiler making the decisions about which instructions to execute in parallel. This approach allowed the processor to execute up to six instructions per clock cycle. By contrast with other superscalar architectures, Itanium did not have elaborate hardware to keep track of instruction dependencies during parallel execution - the compiler had to keep track of these at build time instead.

After a protracted development process, the first Itanium was released in 2001, and more powerful Itanium processors had been released periodically. HP produced most Itanium-based systems, but several other manufacturers had also developed systems based on Itanium.

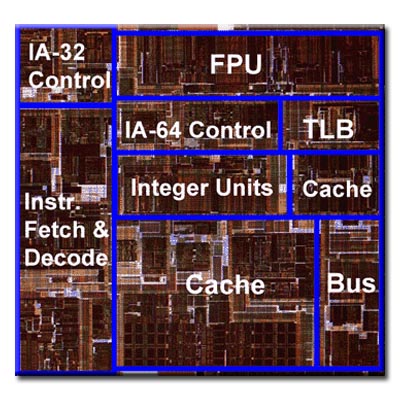

The Merced core

The Itanium processor, code named Merced, was shipped in June 2001. Manufactured in a 180 nm process, it was offered at speeds of 733 and 800MHz, with a choice of 2MB or 4MB off-die L3 cache. In IA-64 mode, it was the fastest floating point processor available in the marketplace. However, on integer calculations it performed only slightly better than an equivalently clocked x86 design, and when running legacy x86 code, performance was only about 1/8th that of a similarly clocked x86 processor. Software emulation (as used later on the Itanium 2) would have been faster.

The main performance limitation with the Itanium processor was the high latency of its level three cache. Intel's engineers had evidently been hoping that the high bandwidth would offset this, but the latency was so high that the cache was not significantly faster than the main memory interface. With the faster first and second-level caches set relatively small (32KB and 96KB respectively), this further increased the load on the main system bus.

Compounding the performance impact of the lack of available cache bandwidth was the fact IA-64 code had a larger footprint than equivalent x86 code, so the number of instructions that could be contained in the cache was even smaller than the sizes alone would suggest. These effects might had been mitigated as Itanium been designed around a fast processor bus. However, at a mere 266MT/s it was only equal to consumer Athlons of the period, and was a full 33% slower than first generation Pentium 4s. This was worse than it would appear, since Itaniums were intended for multiprocessor server systems where system bandwidth is paramount. Itanium clock speeds were also disappointing relative to the GHz speeds being delivered by the x86 architectures of the period.

The technical specifications indicate an original 1998-99 target launch date. The repeated and lengthy project delays meant the processor was out of date before it had began shipping. Hence, the Itanium was not a competitive product when launched, although it would have been two years earlier.

Despite these initial shortcomings, Intel and HP continued their development work. Merced was succeeded by the first Itanium 2 (code-named McKinley) in June 2002.

Source: Wikipedia, the free encyclopedia.