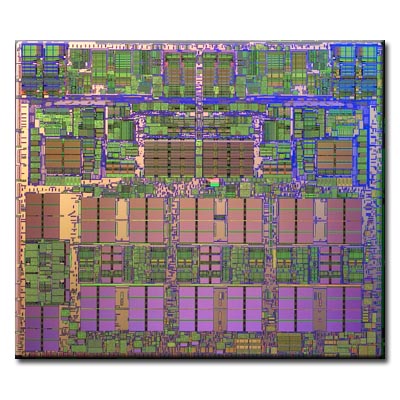

IBM POWER4+ processors

Introduction: May 2003

In May 2003 the pSeries 655 and pSeries 670/690 servers was upgraded with faster POWER4+ processors. For the first time trial/temporary Capacity Upgrade on Demand (CUoD) was available in the pSeries (add processors and/or memory on-the-fly).

The original POWER4 chips were made using a 180 nanometer copper/SOI process. The new dual-core POWER4+ chip was made using a 130 nanometer copper/SOI process resulting in a higher clock speed and a generated heath reduction. The new POWER4+ versions for the pSeries 670/690 machines ran at 1.5GHz and 1.7GHz.

The higher performance of the pSeries 670/690 was also due to the introduction of a new optional RIO-2 (Remote I/O-2) backplane with support for 1 GHz I/O busses that supported 133MHz PCI-X peripheral cards. This resulted in a aggregate I/O bandwidth of 14GB/sec for the pSeries 670 (was 6GB/sec) and 44GB/sec for the pSeries 690 (was 16GB/sec). The new memory cards of the pSeries 670/690 were twice as dense as prior memory cards. Faster L3-cache ran at 567MHz. The pSeries 670 supported up to 256GB of main memory and the pSeries 690 up to 512GB. RIO-2 was also available for the pSeries 650/655.

The 4-8 way pSeries 655 supported the 1.5GHz and the 1.7GHz POWER4+ chip and the existing 1.1GHz and the 1.3GHz POWER4 chip. The machine started shipping by the end of May; upgrades started shipping end of July.

The 4-8-16 way pSeries 670 only supported the POWER4+ chip running at 1.5GHz and the existing 1.1GHz POWER4 chip.

The 8-16-32 way pSeries 690 supported the 1.5GHz and the 1.7GHz POWER4+ chip and the existing 1.1GHz and the 1.3GHz POWER4 chip. The pSeries 670/690 started shipping by the end of May; upgrades started shipping in August.

DLPAR has been improved to support 4 partitions on the pSeries 650/655 (was 2), 16 on the pSeries 670 (was 4) and 32 on the pSeries 690.

Source: rootvg.net